## CP226V-2N4392

## **N-Channel JFET Die**

The CP226V-2N4392 is a silicon N-Channel small signal JFET designed for analog switching and chopper applications.

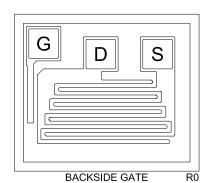

### **MECHANICAL SPECIFICATIONS:**

|                         | î              |

|-------------------------|----------------|

| Die Size                | 20 x 17 MILS   |

| Die Thickness           | 7.1 MILS       |

| Gate Bonding Pad Size   | 3.2 x 3.2 MILS |

| Drain Bonding Pad Size  | 3.2 x 3.2 MILS |

| Source Bonding Pad Size | 3.2 x 3.2 MILS |

| Top Side Metalization   | AI – 30,000Å   |

| Back Side Metalization  | Au – 9,000Å    |

| Scribe Alley Width      | 1.97 MILS      |

| Wafer Diameter          | 5 INCHES       |

| Gross Die Per Wafer     | 45,000         |

| MAXIMUM RATINGS: (T <sub>A</sub> =25°C)    | SYMBOL                             |             | UNITS |

|--------------------------------------------|------------------------------------|-------------|-------|

| Gate-Drain Voltage                         | $V_{\sf GD}$                       | 40          | V     |

| Gate-Source Voltage                        | $V_{GS}$                           | 40          | V     |

| Gate Current                               | $I_{G}$                            | 50          | mA    |

| Operating and Storage Junction Temperature | T <sub>.I</sub> , T <sub>sta</sub> | -65 to +175 | °C    |

## $\textbf{ELECTRICAL CHARACTERISTICS:} \ (T_{\mbox{\scriptsize A}} = 25 \mbox{°C unless otherwise noted})$

| SYMBOL               | TEST CONDITIONS                             | MIN | MAX | UNITS |

|----------------------|---------------------------------------------|-----|-----|-------|

| <sup>I</sup> GSS     | V <sub>GS</sub> =20V                        |     | 0.1 | nA    |

| I <sub>DSS</sub>     | V <sub>DS</sub> =20V                        | 25  | 75  | mA    |

| <sup>I</sup> D(OFF)  | $V_{DS}$ =20V, $V_{GS}$ =7.0V               |     | 0.1 | nA    |

| BVGSS                | I <sub>G</sub> =1.0μA                       | 40  |     | V     |

| V <sub>GS(OFF)</sub> | V <sub>DS</sub> =20V, I <sub>D</sub> =1.0nA | 2.0 | 5.0 | V     |

| $V_{GS(f)}$          | $V_{DS}$ =0, $I_{G}$ =1.0mA                 |     | 1.0 | V     |

| V <sub>DS(ON)</sub>  | I <sub>D</sub> =6.0mA                       |     | 0.4 | V     |

| rDS(ON)              | $I_D=1.0$ mA, $V_{GS}=0$                    |     | 60  | Ω     |

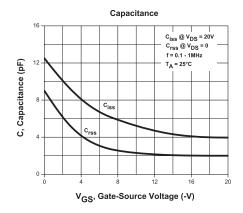

| C <sub>rss</sub>     | $V_{GS}$ =7.0V, $V_{DS}$ =0, f=1.0MHz       |     | 3.5 | pF    |

| C <sub>iss</sub>     | $V_{DS}$ =20V, $V_{GS}$ =0, f=1.0MHz        |     | 20  | pF    |

| ton                  | $I_{D(ON)}=6.0$ mA                          |     | 15  | ns    |

| t <sub>off</sub>     | V <sub>GS(OFF)</sub> =7.0V                  |     | 35  | ns    |

# CP226V-2N4392

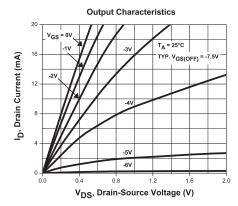

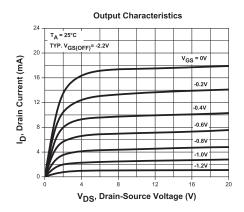

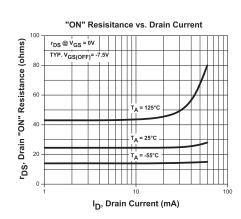

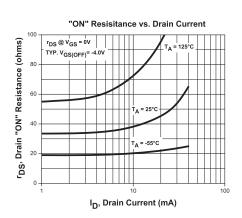

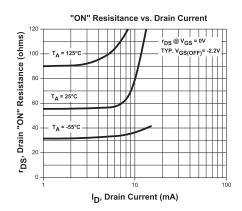

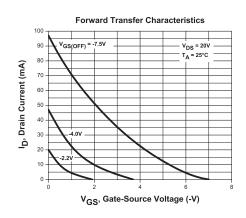

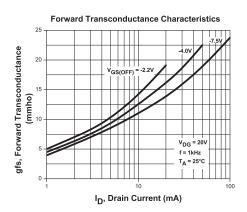

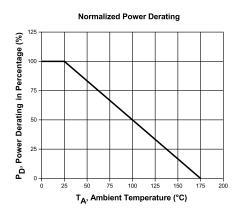

## **Typical Electrical Characteristics**

www.centralsemi.com

R0 (24-February 2021)

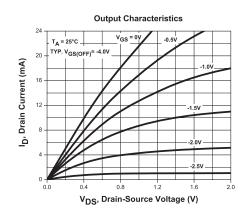

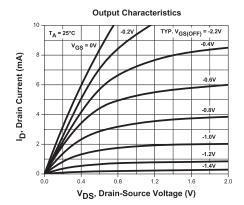

# CP226V-2N4392

## **Typical Electrical Characteristics**

R0 (24-February 2021)

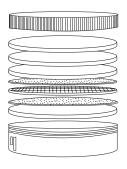

### BARE DIE PACKING OPTIONS

## BARE DIE IN TRAY (WAFFLE) PACK

CT: Singulated die in tray (waffle) pack. (example: CP211-PART NUMBER-CT)

CM: Singulated die in tray (waffle) pack 100% visually inspected as per MIL-STD-750, (method 2072 transistors, method 2073 diodes). (example: CP211-PART NUMBER-CM)

### **UNSAWN WAFER**

WN: Full wafer, unsawn, 100% tested with reject die inked. (example: CP211-PART NUMBER-WN)

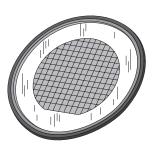

#### SAWN WAFER ON PLASTIC RING

**WR**: Full wafer, sawn and mounted on plastic ring, 100% tested with reject die inked.

(example: CP211-PART NUMBER-WR)

Please note: Sawn Wafer on Metal Frame (WS) is possible as a special order. Please contact your Central Sales Representative at 631-435-1110.

Visit the Central website for a complete listing of specifications: www.centralsemi.com/bdspecs

R2 (3-April 2017)

### **OUTSTANDING SUPPORT AND SUPERIOR SERVICES**

#### PRODUCT SUPPORT

Central's operations team provides the highest level of support to insure product is delivered on-time.

- Supply management (Customer portals)

- · Inventory bonding

- · Consolidated shipping options

- · Custom bar coding for shipments

- · Custom product packing

#### **DESIGNER SUPPORT/SERVICES**

Central's applications engineering team is ready to discuss your design challenges. Just ask.

- Free guick ship samples (2<sup>nd</sup> day air)

- Online technical data and parametric search

- SPICE models

- · Custom electrical curves

- · Environmental regulation compliance

- · Customer specific screening

- · Up-screening capabilities

- Special wafer diffusions

- PbSn plating options

- Package details

- Application notes

- · Application and design sample kits

- Custom product and package development

#### REQUESTING PRODUCT PLATING

- 1. If requesting Tin/Lead plated devices, add the suffix "TIN/LEAD" to the part number when ordering (example: 2N2222A TIN/LEAD).

- 2. If requesting Lead (Pb) Free plated devices, add the suffix "PBFREE" to the part number when ordering (example: 2N2222A PBFREE).

#### **CONTACT US**

#### Corporate Headquarters & Customer Support Team

Central Semiconductor Corp. 145 Adams Avenue Hauppauge, NY 11788 USA

Main Tel: (631) 435-1110 Main Fax: (631) 435-1824

Support Team Fax: (631) 435-3388

www.centralsemi.com

Worldwide Field Representatives: <a href="https://www.centralsemi.com/wwreps">www.centralsemi.com/wwreps</a>

**Worldwide Distributors:**

www.centralsemi.com/wwdistributors

For the latest version of Central Semiconductor's **LIMITATIONS AND DAMAGES DISCLAIMER**, which is part of Central's Standard Terms and Conditions of sale, visit: <a href="https://www.centralsemi.com/terms">www.centralsemi.com/terms</a>

www.centralsemi.com (001)